| 单位名称 | 北京思朗科技有限责任公司 | 单位性质 | 民营企业 |

|---|---|---|---|

| 单位地址 | 北京市海淀区 | 单位行业 | 信息传输、软件和信息技术服务业 |

| 单位规模 | 100-299人 | 单位网址 |

| 学历要求 | 本科生,硕士生,博士生 | 招聘总人数 | 20 | 研究生人数 | 10 | 本科生人数 | 10 |

|---|

| 简历接收邮箱 | 网申地址 | https://xiaoyuan.zhaopin.com/company/CC000618513D90000000000 |

|---|

北京思朗科技有限责任公司校园招聘简章

思朗科技由前国家集成电路工程技术中心主任、中科院自动化所所长王东琳先生于2016年创立,是国内领先的处理器内核研发、芯片设计、软件应用开发和密集计算机整机供应商。 公司主要业务模式为密集计算领域的处理器内核研发、芯片设计、软件应用开发和密集计算整机销售,其核心优势在于自主研发的架构,该架构是通用计算架构领域的重大创新,是全球首个可重构的芯片架构设计。该架构的提出,领先于2017年美国DARPA支持的电子复兴计划架构——软件定义硬件(SDH)和特定域片上系统(DSSoC)8年时间,实现了中国在密集计算芯片领域的完全自主可控。 我们追求打造极致的产品,秉承客户至上的原则,在实现商业化的道路上正稳步快速前进。

一、校招流程:

网申(只接受网申)—面试—签三方—实习机会

温馨提示:我们将分批处理,具体面试时间会微信或电话通知,感谢关注。

二、招聘岗位:

Ø ASIC数字设计岗(北京)

岗位职责:

1. 负责模块的实现方案编写或验证方案编写;

2. 负责模块的RTL代码实现;

3. 负责模块仿真过程中RTL代码或验证环境的问题定位及解决。

岗位要求:

1. 本科以上学历,集成电路、通信、计算机及其他理工类专业;

2. 有数字逻辑设计/时序电路基础知识和基本技能;

3. 熟练掌握verilog语言;

4. 了解SystemVerilog/UVM验证方法学、数字电路的综合和静态时序分析、具备无线通信、视频图像处理相关知识者优先。

Ø ASIC数字验证岗(北京)

岗位职责:

1. 开发与维护SOC以及模块的验证环境与用例;

2. 编写并执行验证计划,完成验证报告等。

岗位要求:

1. 具有数字集成电路基础知识,了解芯片设计、验证流程,熟悉systemverilog UVM SVA C等;

2. 集成电路、微电子、软件类相关专业硕士及以上学历。

Ø 工具链开发岗(北京)

岗位职责:

1. 自研芯片C/C++编译器,模拟器,调试器研发和维护。

岗位要求:

1. 熟悉C/C++编程,熟悉linux环境;

2. 了解处理器架构,有编译器,模拟器,调试器优先;

3. 良好的学习能力,良好的沟通能力和团队合作精神;

4. 计算机、软件类相关专业本科及以上学历。

Ø 工具链测试岗(北京)

岗位职责:

1. 自研芯片工具链及相关工具的测试设计,实施和分析等工作。

岗位要求:

1. 熟悉C/C++语言或java, python语言;

2. 了解各种测试方法,linux操作,shell和makfile;

3. 了解CI/CD/DevOps理论以及常用的工具,如jenkins、git、nexus等优先;

4. 良好的学习能力,良好的沟通能力和团队合作精神;

5. 计算机、软件类相关专业本科及以上学历。

Ø SDK开发岗(北京)

岗位职责:

1. 自研芯片的SDK及相关工具的研发和维护。

岗位要求:

1. 熟悉java/c/shell等编程语言;

2. 了解Eclipse平台,了解Eclipse插件开发及常用的开源插件,包括但不限于Eclipse CDT、Eclipse embed-cdt等优先;

3. 良好的学习能力,良好的沟通能力和团队合作精神;

4. 计算机、软件类相关专业本科及以上学历。

Ø 微处理器数字集成电路设计岗(北京)

岗位职责:

1. 微处理器相关部件的RTL设计实现及优化;

岗位要求:

1. 掌握数字集成电路基础知识,熟悉芯片设计流程,有综合、验证、STA经验者优先;

2. 熟悉微处理器结构,有处理器设计经验、汇编开发或调试经验者优先;

3. 有门级逻辑设计经验者优先;

4. 集成电路、微电子、电子类相关专业本科及以上学历。

Ø 数字集成电路设计岗(北京)

岗位职责:

1.参与内核指令集定义;

2.参与Fetch、Cache、计算单元、Load/Store单元等子系统的RTL设计、优化等工作;

3.配合验证、算法等相关部门完成指令功能及性能优化;

4.参与SDC设计,配合实现部门完成Synthesis、DFT、STA等;

岗位要求:

1.通信.电子.计算机等相关专业硕士及以上学历;

2.数字电路设计和验证相关实习经验;

3.熟练掌握Verilog和相关仿真环境; 有一定的脚本开发能力(python.perl.shell);

4.良好的沟通能力和团队合作精神;

Ø 数字后端设计岗(北京)

岗位职责:

1. 负责数字电路从网表到GDS的后端设计工作,包括布局布线、时钟树综合等。

岗位要求:

1. 微电子、集成电路等相关专业,硕士及以上学历;

2. 具有数字集成电路基础知识,熟悉芯片后端设计流程,了解synopsys/cadence 等EDA设计工具。

Ø 可测性设计岗(DFT)(北京)

岗位职责:

1. 负责芯片DFT设计的实施,包括scan/mbist的设计,测试向量生成,验证等;

2. 协助芯片的ATE测试。

岗位要求:

1. 微电子、集成电路等相关专业,硕士及以上学历;

2. 具备可测性设计的理论知识和概念,熟悉DFT技术和设计流程,熟悉DFT相关的设计工具。

Ø DSP软件岗-超算/通信/AI加速(北京)

岗位职责:

1. 负责基于自研架构DSP的超算/AI加速/5G物理层模块并行实现方案设计及代码实现;

2. 负责所开发模块的单元测试及文档编写;

3. 协助模块集成及系统应用调试。

岗位要求:

1. 具有良好的数字信号处理基础优先;

2. 熟悉C语言;

3. 计算机、各类型工科专业硕士及以上学历。

Ø 系统应用岗-超算/AI加速(北京)

岗位职责:

1. 负责基于自研架构DSP的超算/AI加速系统应用整体解决方案开发;

2. 负责所开发解决方案的集成测试、系统测试;

3. 负责所开发超算/AI加速系统的文档编写;

岗位要求:

1. 具有良好的数学/数字信号处理基础优先;

2. 熟悉C语言,了解过汇编语言优先;

3. 计算机、各类型工科专业硕士及以上学历。

Ø 应用算法岗(北京)

岗位职责:

1. 负责研究领域算法,对算法和系统性能进行评估;

2. 构建分布式计算数学模型,实现领域计算在分布式计算系统上的计算;

3. 为计算系统实现提供解决方案,负责与外部科学合作团队对接。

岗位要求:

1. 研究生及以上学历,化学工程专业或电子信息方向专业;

2. 下列两项具备其一:

(1)熟悉分子动力学/分子对接/药物筛选计算模拟相关方向的计算方法及原理,有代码实现经验;

(2)熟悉流体力学相关方向的计算方法及原理,有代码实现经验;

3. 熟练掌握matlab/C/C++/Fortran编程中的一种或多种;

4. 有良好的数学基础,对计算系统的实现有强烈兴趣,具备优秀的学习能力。

Ø 算法开发岗(北京)

岗位职责:

1. 负责领域算法定点化开发、性能验证和校准;

2. 负责领域算法在自研处理器的实现对接。

岗位要求:

1. 电子信息或相关等专业研究生及以上学历,有良好的数学基础;

2. 有算法开发经验,有定点化工作经验;

3. 熟练掌握matlab/C编程。

Ø 5G物理层基带开发岗(北京、西安)

岗位职责:

1. 负责5G基带芯片物理层软件设计与集成开发;

2. 负责5G基带芯片物理层软件设计与集成开发;

3. 负责5G基带芯片商用过程中的新功能开发、性能可靠性等问题的定位解决。

岗位要求:

1. 通信类相关专业硕士以上学历;

2. 具有DSP 开发经验,尤其是多核DSP开发经验,熟悉DSP程序开发流程;

3. 熟悉4/5G 物理层协议,了解物理层实现关键算法。

Ø 嵌入式驱动开发岗(北京、西安)

岗位职责:

1. 通信产品驱动开发和调试;

2. Linux系统移植;

3. 开发文档编写。

岗位要求:

1. 精通C语言;

2. 熟悉常见嵌入式微处理器的内部架构;

3. 有linux用户态编程经验;

4. 熟悉shell脚本与Makefile;

5. 通信类相关专业硕士以上学历,有通信产品开发经验优先;

6. 良好的学习能力,沟通能力和团队合作精神。

Ø 算法岗(北京)

岗位职责:

1. 负责跟踪和了解最新通信技术发展以及行业标准演进;

2. 负责研究和仿真通信算法和通信系统,对算法和系统性能进行评估;

3. 负责对算法进行定点化,为实现算法做支持;

4. 为通信系列芯片发展提供产品路线规划以及性能、功能需求分析;

5. 为通信系统实现提供解决方案。

岗位要求:

1. 通信或相关专业,研究生及以上学历;

2. 熟悉移动通信物理层基带处理算法,有5G PUSCH/PUCCH/PRACH/SSB/PDSCH/PDCCH一到多条信道开发经验为佳;

3. 熟悉LDPC/Polar编译码算法为佳;

4. 熟练掌握C/C++/Matlab编程;

5. 工作态度积极,善于学习,有较强的团队合作精神。

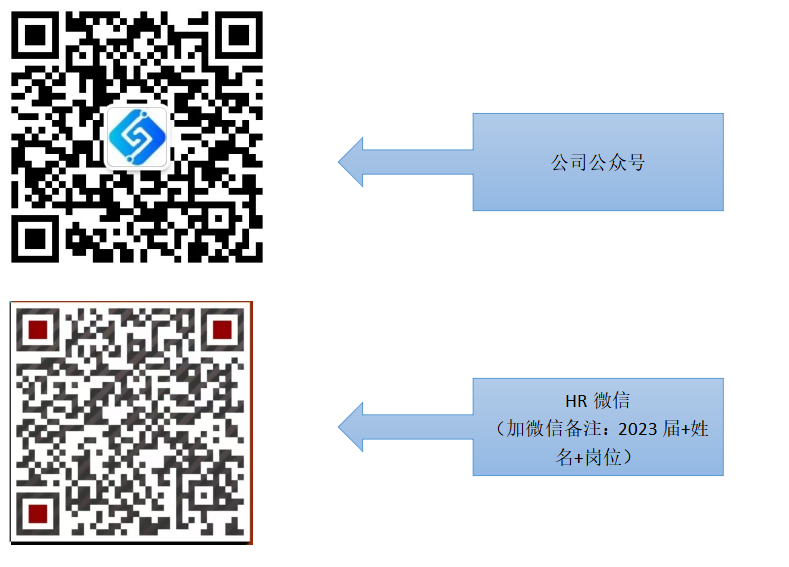

三、联系方式:

Ø 公司网址:http://www.smartlogictech.com/

Ø 公司电话: 010-82544469(人力资源部)

Ø 公司地址:

北京:北京市海淀区中科爱克大厦;

西安:西安市高新区汇诚国际。